GIACOMO VALENTE, Università degli Studi dell'Aquila, Italy TIZIANA FANNI, Università degli Studi di Sassari, Italy CARLO SAU, Università degli Studi di Cagliari, Italy TANIA DI MASCIO, Università degli Studi dell'Aquila, Italy LUIGI POMANTE, Università degli Studi dell'Aquila, Italy FRANCESCA PALUMBO, Università degli Studi di Sassari, Italy

Advanced computations on embedded devices are nowadays a must in any application field. Often, to cope with such a need, embedded systems designers leverage on complex heterogeneous reconfigurable platforms that offer high performance, thanks to the possibility of specializing/customizing some computing elements on board, and are usually flexible enough to be optimized at run-time. In this context, monitoring the system has gained increasing interest. Ideally, monitoring systems should be non-intrusive, serve several purposes and provide aggregated information about the behaviour of the different system components. However, current literature is not close to such ideality: for example, existing monitoring systems lack in being applicable to modern heterogeneous platforms. This work presents a hardware monitoring system, which is intended to be minimally invasive on system performance and resources, composable and capable of providing to the user homogeneous observability and transparent access to the different components of a heterogeneous computing platform, so that system metrics can be easily computed from the aggregation of the collected information. Building on a previous work, this paper is primarily focused on the extension of an existing hardware monitoring system to cover also specialized coprocessing units, and the assessment is done on a Xilinx FPGA-based System on Programmable Chip. Different explorations are presented to explain the level of customizability of the proposed hardware monitoring system, the trade-offs available to the user, and the benefits with respect to standard de-facto monitoring support made available by the targeted FPGA vendor.

CCS Concepts: • **Computer systems organization**  $\rightarrow$  **Embedded systems**; *Redundancy*; Robotics; • **Networks**  $\rightarrow$  Network reliability.

Additional Key Words and Phrases: HW Monitoring, Monitoring system, Heterogeneous system, HW Reconfiguration, FPGA

#### **ACM Reference Format:**

Giacomo Valente, Tiziana Fanni, Carlo Sau, Tania Di Mascio, Luigi Pomante, and Francesca Palumbo. 2018. A composable monitoring system for heterogeneous embedded platforms. *J. ACM* 37, 4, Article 111 (August 2018), 33 pages. https://doi.org/10.1145/1122445.1122456

Authors' addresses: Giacomo Valente, Università degli Studi dell'Aquila, L'Aquila, Italy, giacomo.valente@univaq.it; Tiziana Fanni, Università degli Studi di Sassari, Cagliari, Italy, tfanni@uniss.it; Carlo Sau, Università degli Studi di Cagliari, Cagliari, Italy, carlo.sau@unica.it; Tania Di Mascio, Università degli Studi dell'Aquila, L'Aquila, Italy, tania.dimascio@univaq.it; Luigi Pomante, Università degli Studi dell'Aquila, L'Aquila, Italy, luigi.pomante@univaq.it; Francesca Palumbo, Università degli Studi di Sassari, Cagliari, Italy, luigi.pomante@univaq.it; Francesca Palumbo, Università degli Studi di Sassari, Cagliari, Italy, fpalumbo@uniss.it.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2018 Association for Computing Machinery.

0004-5411/2018/8-ART111 \$15.00

https://doi.org/10.1145/1122445.1122456

111

#### **1 INTRODUCTION**

System monitoring is typically an application- and platform-specific process, especially when dealing with embedded systems. By definition, a generic monitoring process, implemented by a proper monitoring system, has the goal of satisfying some given monitoring requirements (those for the design of a monitoring system [31]), which turns out into gathering system representative metrics [19]. Traditionally, designers have been using custom methodologies and monitoring systems to evaluate the metrics of interest, exploiting ad-hoc Hardware (HW)/Software (SW) components and infrastructures to make such metrics observable by the designer and/or by the system itself. HW monitoring systems, preferable to SW since they minimally affect the execution performance, are intended as the physical components needed in the design to gather information from system resources (e.g., cores, memories, coprocessing units. etc.). The definition of ad-hoc solutions, optimized for a given platform [6, 46] or on metrics [11, 30], typically fails in being portable to other platforms, technologies, and/or contexts.

The problem of defining effective and efficient HW monitoring systems, with small engineering effort, has become more complex in modern heterogeneous devices. To support variable workloads and to address several and concurrent functional and non-functional requirements, modern platforms tend to integrate different types of resources. Different cores and/or application-specific units are adopted, but also configurable logic is often brought on-board. Field Programmable Gate Array (FPGA) devices, traditionally employed for rapid prototyping and low-volume application purposes, are gaining momentum in production (e.g., Lattice Semiconductor FPGA in edge devices [1]). The continuous increase in the computational demand required by modern applications, coupled with flexibility requirements typical of Cyber-Physical Systems (CPSs), began to show the limits of traditional general-purpose SW-programmable platforms. Customizability upon the application needs makes FPGA-based System on a Programmable Chip (SoPC) particularly suitable to this context. Nevertheless, having available these many degrees of freedom certainly complicates the monitoring process. The monitoring system needs not only to gather information to evaluate different kinds of metrics (e.g., number of cache misses, number of clock cycles to execute HW or SW tasks) and to access different types of resources (e.g., the memory), but it also needs to be configurable enough to be customized upon designer requests, possibly with minimal effort for the user. To the best of our knowledge such a desirable monitoring infrastructure does not exist yet, despite the problem is known since a while. Back in 2013, Kornaros et al. [19] already expressed this lack, surveying the existing monitoring systems for multi-core Systems on Chip (SoCs), and trying to identify the motivations behind it. In Kornaros' work a taxonomy for the formalization of the monitoring problem was proposed and discussed. The concept of event to be monitored turned out to be not really well defined, and a lot of subjectivity was there due to the fact that "different observers can describe the same event in different terms, and may assume different sources of the cause, or of the location, or of the time of the event monitoring in general". Such a lack and the need for overcoming the diversity of solutions, brought by the designer-subjectivity or by the heterogeneity of monitored metrics and platforms/components, which is particularly true in the context of heterogeneous FPGA SoPCs, are the major drivers behind this work.

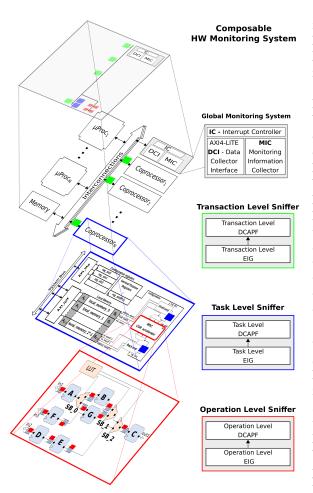

In this paper, we propose a composable HW monitoring system for heterogeneous embedded platforms able to gather information from different system resources to allow gathering information from all the different components composing a traditional heterogeneous systems, which will allow afterwards for system-level metrics evaluation. In particular:

• Following a brick-based principle, different system resources at different abstraction levels are made observable by the proposed HW monitoring system. Each system resource/level is observed through distributed *sniffers* able to get the monitoring information and to aggregate

them in a common data structure easily accessible by the user (e.g., a designer, a run-time manager): sniffers are composable and, together with their collected information and their final structure, represents the monitoring system. *Composability, i.e. the possibility of observing different system resources operating at different levels of abstraction, is a key feature of the proposed approach.*

- The proposed HW monitoring system is a unifying solution that makes observable both HW and SW Intellectual Propertys (IPs). Furthermore, the collected monitoring information is accessible through Application Program Interfaces (APIs), guaranteeing that the events are properly captured and that the information is correctly propagated through the SW stack, no matter where they have been extracted from. *Homogeneous observability and access provided by the sniffers at different layers is a key feature of the proposed approach.*

- The proposed HW monitoring system is based on a configurable number of distributed sniffers, enabling a high degree of customization in terms of observed interconnections and metrics to be gathered. No matter to which resource they are attached to, sniffers have always the same internal architecture. These features enable the reuse of blocks among different sniffers by means of a library-based approach. *System observation is more straightforward. Sniffers can be re-used and easily customized to gather new information from new system parts.*

- The proposed approach is fully passive. The actions and elements needed to gather information from the system are decoupled from those using the gathered information. In this work, we focus on the Event Instance Generation, Data Capture and Data Filtering steps of the *generic monitoring process* introduced in [19]. Decoupling the passive observation action from the active reaction one allows a more generic definition of the HW monitoring system and to make it reusable for different purposes over different platforms. *The heterogeneous system, despite its complexity and target application, is made entirely observable.*

The rest of this paper is organized as follows. Section 2 describes more in details the reference scenario and, in particular, the family of targeted computing platforms. Moreover, it explores also the state of the art, highlighting the contributions/advances of this paper in the provided boxes. Section 3 illustrates our composable HW monitoring system for heterogeneous embedded platforms. Section 4 discusses the carried out assessments, before the final remarks provided in Section 5.

## 2 MONITORING HETEROGENEOUS SYSTEMS: CONTEXT AND BACKGROUND

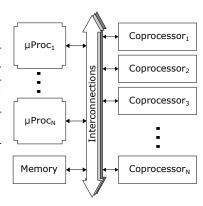

The advent of SoPCs allowed for the definition of powerful embedded computing platforms that combine the high-level management capabilities of microprocessors with the high performance. Concepts as FPGA overlays and FPGA companion computers are nowadays extremely popular [9, 43]. They are addressed in many studies that target HW/SW systems [20, 32, 36] that aim to couple microprocessors with HW accelerators, which may also offer different levels of reconfigurability [14]. This introduces the need for having visibility at various levels of the computing infrastructure. Figure 1 depicts a high-level schematic overview of the target reference architecture that we consider in this work that can present one or more microprocessors, one or more coprocessors, and a memory that shares data by means of one or more intercon-

nection buses. Here with coprocessors we intend dedicated Fig. 1. Baseline reference architecture. hardware accelerators, which can be either fixed function or reconfigurable ones, loosely coupled

with the host microprocessors by means of the generic system interconnection (meaning that a unique bus line, or parallel bus lines, can be used to better handle data and control signals). A tightly coupled version of the work, where coprocessors are accessible through exclusive, more efficient connections is left to future extensions. Monitoring infrastructures are already integrated in fixed architectures [6], and HW performance counters are a built-in feature of all modern microprocessors, allowing for low-level performance analysis or tuning. Nevertheless, dealing with heterogeneity makes the problem of system observability more complex. At the time being, the state of the art around FPGA overlays and FPGA companion computers is still young [23, 43] and established design and programming solutions are not there yet [22]. One of the reasons is that the programmable part is quite always shaped according to the considered problem, and this inevitably impacts also on the adoptable HW monitoring system. A widely applicable solution embracing all of the components of the architecture, and allowing for a homogeneous observability and access to all the components, is not there yet. That is the motivation at the basis of this work. Times are mature enough to start defining a more comprehensive metric agnostic HW approach. In the rest of this section, state of the art approaches are discussed in Section 2.1, then the contributions of the proposed work in this context are summarized in Section 2.2.

## 2.1 Related Works

Several reasons for monitoring heterogeneous systems exist: e.g., to guarantee the correct execution of a device and the right communication among its elements, to gather statistics used in subsequent system re-design cycles, to understand run-time performance and check whether any room for optimization is there. Such a proliferation of needs led designers to cope with them with different solutions which turned out to be as heterogeneous as the systems they want to monitor. The lack of standardization and homogeneity of methodologies and purposes was analysed for the first time in 2013 by Kornaros et. al [19]. Authors tried to classify the monitoring techniques according to their purpose: Debug, Performance, Quality-of-Service, Power related, Fault Tolerance and Reliability, Security and Others. Most of the works they analysed adopt vertical approaches (as [37, 39, 40] in Table 1), but in nowadays complex and heterogeneous systems such classification may fail. Indeed, in current systems different aspects and purposes are monitored concurrently, which may imply accessing different architectural components at the same time. Kornaros et al. concluded their analysis with an open challenge: *"to understand the exact robustness, performance, and complexity characteristics of integrating diverse HW components together with SW tasks with varying behaviour"*.

The issue of heterogeneity mastering is still there and when microprocessors are coupled to embedded reconfigurable units the problem is even more severe. Designers shall tackle both the heterogeneity of the infrastructure and of some of the elements of the infrastructure over time. Indeed, the coprocessing units may change their internal structure over time, depending on the tasks to be executed, leveraging on the reconfiguration capabilities of the FPGA.

In the following, we analyse and discuss different monitoring strategies available in literature, with the intent of classifying them in terms of monitored resources. We consider only those works that address one or more elements present in our reference architecture (see Figure 1) and we also provide information regarding the purpose at the base of their monitoring needs. To simplify the classification, we grouped Kornaros' purposes as follows: Performance (including also Profiling and Quality of Service), Debug and Verification (including also Run-time Verification, Fault Tolerance and Reliability), Power (including also Energy and Temperature), and Security. Table 1 depicts a schematic overview of the considered monitoring strategies, including the one presented in this paper.

Many works available in literature focus on microprocessor monitoring. Nelissen et al. [31] and Seo et al. [40, 41] focus on monitoring it for verification purposes. Nelissen et al. present an architecture for the implementation of a safe and reliable monitoring framework for run-time SW verification. Seo et al. in [40] propose a Trace Abstraction Layer and show a methodology that can perform verification using the Micron Automata Processors, while in [41] authors show a methodology that can drive a designer from requirements to the configuration of a hardware monitoring system for runtime verification, targeting the SW running on microprocessors. Similarly, Rambo et al. [35] adopt the Trace Abstraction Layer for verification and performance monitoring, discussing different techniques for information processing factory that make it a suitable solution for highly dependable systems. Different researches in literature developed strategies of HW profiling intended to foster SW optimization or system self-adaptation. Aldham et al. [4] presented LEAP, a HW profiler for FPGA-based embedded microprocessors, where gathered information is used to improve both performance and HW/SW partitioning. To improve this latter, Nadimpalli et al. [29] proposed another profiler capable of identifying high computational loads to be moved to HW execution. Scheipel et al. [39] present an approach for measuring execution time and events of an embedded system by integrating a dedicated performance monitoring infrastructure using HW/SW co-design techniques; on the other hand, Sadek et al. [37] propose another infrastructure called STHEM, which is a collection of utilities for heterogeneous embedded image processing platforms. STHEM features also a power measurement utility that enables programmers to correlate instantaneous power samples with concurrent HW/SW traces, gathered through the Xilinx SW debugger.

Despite the heterogeneity of their purposes, these microprocessors monitoring systems do not address the other components of the adopted reference architecture. Moreover, to the best of our understanding, the kind of monitored events and used monitors would make them hardly tuneable to gather different information from other components in a composable manner.

Monitoring the microprocessor is not sufficient to offer a complete system observability. Patrigeon et al. [34] present an FPGA-based platform, instrumented with monitors, for real-time evaluation of Ultra Low Power SoCs. The microprocessor interacts with the monitors as with common peripherals, connected by means of the Advanced High-performance Bus lite system. The monitors gather events related to the memory execution and are enabled, disabled, and reset through SW function calls. Doyle et al. [13, 25] present ABACUS, a HW framework that leverages on the FPGA reconfigurable fabric to monitor the workload execution. To foster ABACUS portability to different architectures and the extension with profiling units, microarchitecture independent metrics are supported. Also, a trade-off analysis between application performance and amount of data gathered is performed. The work of Valente et al. [27, 44], apart from the fact that is able to monitor also the interconnection, introduces also the flexibility in monitoring through the definition of a custom profiling system for embedded applications: their work split the monitor design in a number of sub-blocks (stored in a library), each one implementing a part of a generic profiling action.

All the above-mentioned works use monitoring for SW performance understanding only, and the considered reference architecture is still not a heterogeneous one. Nevertheless, Doyle et al. and Valente et al., with a library of customizable monitors, moved some steps towards the concepts of a wider applicability of the monitoring components to different resources/architectures.

Similarly to memories, also the communication elements have been addressed as monitoring object. Kyung et al. [26] presented the first monitor for the Advanced eXtensible Interface (AXI) bus, and Xilinx provides a dedicated monitor for AXI4 connections, the AXI Performance Monitor [46]. It can be added to the design to measure major transaction-related metrics.

These communication-oriented solutions are limited by construction, being highly componentspecific, but are certainly complementary to others.

The ARM Coresight [6] is a commercial solution for the debug and trace of complex SoCs. It eases the monitoring of the data infrastructure, providing a library of modular components, for the monitoring of CPU, memory and communication elements, generalizing the access to the monitors.

One of the most interesting aspects of the ARM Coresight approach is that data gathering, from the SW perspective, is made homogeneous despite the monitored components. This is an appealing aspect, that goes towards the same attempt of access homogenization that we are pursuing in this work. Nevertheless, as it should be expected, the Coresight is conceived for a fixed infrastructure, and no (re-)configurable coprocessing units are taken into consideration.

The advent of FPGA-based SoCs opened up a plethora of new opportunities in the computing domain and, from the monitoring perspective, it introduced coprocessors as new elements to be monitored. SW monitoring could serve to identify parts of the application that benefit from a HW implementation [4, 29] and some works address FPGA-based platforms [25, 34, 44], despite they do not give a comprehensive monitoring for such systems. To enable observability, FPGA vendors, such as Xilinx and Intel, are making available solutions to monitor SoC [5, 45, 46]. Besides AXI Performance Monitor, intended for buses, Xilinx provides also the System Integrated Logic Analyzer (ILA) [45] while Intel has the similar Signal Tap Logic Analyzer [5], both for debug purposes.

In all these cases, the internal signals and interfaces are monitored, requiring high HW expertise since no API calls are available. Moreover, these techniques are conceived for the programmable logic only. They could be combined with other approaches, but fail in providing a widely re-usable and applicable solution. Finally, they are vendor-specific. To address the problem of monitoring from a more general perspective, the level of abstraction has to be risen, and vendor-specific approaches are not generally suitable for this.

To raise the level of abstraction and offer a user-friendly monitoring system suitable for SW developers, Goeders et al. [16] presented a High Level Synthesis (HLS) tool for the instrumentation of monitors for debugging. Their work has been demonstrated on the LegUp HLS [10] and, starting from a C++ description, both systems and monitors are derived. Hammouda et al. [17] provide an HLS tool that, starting from a C description, automatically generates the HW system instrumented with monitors for run-time verification. To provide a SW developer-friendly approach, and to monitor also coprocessing units, Fanni et al. [15, 24] extended the Performance Application Programming Interface [33], developing a configurable component for reading monitors within an application-specific coprocessor. They also propose a toolchain that instruments the HW coprocessors, generates the configuration file for the component (compliant with the Performance Application Programming Interface), and provides the APIs to initiate and read the monitors in the HW coprocessors, as the ones normally present on every CPU.

HLS-based approaches are capable of overcoming the problem of low level details management. They could potentially be extended to cover all the elements of our reference architecture. Nevertheless, to the best of our knowledge, such extensions have not been developed yet.

By looking at the monitoring issue from a high level perspective, the work of Lee et al. has to be mentioned. They proposed in [21] a system-level observation framework for the run-time analysis and verification of both SW and HW tasks without perturbing the system execution. In this work, a concrete step ahead towards a formalization of the monitoring process and the definition of a generalizable monitoring method is made. Monitors are built upon sets of customizable observation probes that can be adapted to monitor both microprocessors and coprocessing units. This work

draws attention on the connection between the goal of the monitoring, which in the paper is debugging, and the low-level event types. Moreover, the event-generation process from "what is monitored" is considered as a fundamental activity in building the monitoring infrastructure.

Lee's work represents a step ahead in the generalization of a monitoring action for run-time verification, even if it focuses only on microprocessor and coprocessor (no details about the types of supported coprocessors are provided). It defines the HW/SW observation interfaces to gather the data from the coprocessing elements, but not the details on how events are captured.

To the best of our knowledge, only two literature works seemed to be capable of targeting all the components of the adopted reference architecture. Both Najem et al. [30] and Zoni et al. [11] are focused on power monitoring only, exploiting machine learning techniques, applied over the Register Transfer Level (RTL) description of the system.

These methodologies address all the components of the reference architecture as the present work is doing, but portability towards other monitoring purposes seems to be impractical and would require a complete re-engineering of the discussed methodologies to enable a completely different set of metrics/statistics gathering. Basically, to the best of our understanding, despite these works are capable of feeding back at system level power-related information, the authors never tried to generalize the monitoring system to define a broader applicable methodology out of the engineering work done for power estimations.

## 2.2 Key Remarks and Summary of Contributions

Based on our studies we derived a list of features that an ideal monitoring system should present:

- (1) It should be *minimally invasive* with respect to resources (with a low overhead on the programmable logic), to the nominal behaviour (execution should be not slowed down) and to the memory occupancy of the monitored system.

- (2) It should be applicable to monitor functionalities on SW and HW in a seamless manner, which is why the proposed HW monitoring system intends to provide *homogeneous observability*.

- (3) It should be flexible enough to gather information from different system components to evaluate different metrics. The HW monitoring system should be easily extendable and re-usable, and built to facilitate *heterogeneous information aggregation*.

- (4) From the SW developer perspective, the access to the monitoring infrastructure should be as simple as an API call, no matter where the monitored task is executed. Lower level details on how events are observed and captured and on the involved components should be transparent to the user, thus providing *homogeneous access* to the monitoring process and data.

- (5) It should be coupled to a framework/tool to enable a fast and possibly automatic integration of the monitoring infrastructure within the target system and within the executing code. Indeed, a *user friendly* design environment has to be provided.

This list is quite aligned with other lists of desiderata for monitoring systems in literature [18]. Nevertheless, the considered works (Table 1) lack in trying to embrace cross-purpose aspects and mix observability and controllability of the passive and active monitoring activities that we are trying to decouple. Moreover, the heterogeneity of the components has not been addressed.

The proposed HW monitoring system for heterogeneous FPGA-based SoPCs targets all the components of the reference architecture in Figure 1. The monitoring components are built in a similar manner, thanks to the customization capabilities of the monitors that can be specialized for the events to be captured, but the APIs used to report the information at system level are the same. Moreover, designers can play with different customization options trading off monitoring overhead (in terms of resources, time and memory) versus the observation capabilities according to

Table 1. Related Works Classification:  $\mu Proc$ , *Mem.*, *Comm.* and *Copr.* are respectively Microprocessor, Memory, Communication and Coprocessor. [<sup>a</sup> This paper extends previous works of Valente et al. [27, 44], where microprocessor, memory and interconnection monitoring capabilities have already been demonstrated. Nevertheless, monitoring capabilities of the proposed system are proved for microprocessor, coprocessor and communication (see Transaction Level within the coprocessor).

| 1 | <sup>b</sup> Quantitative results comparison with respect to this work is presented in Section 4. <sup>c</sup> $D\&V$ stands for Debug |

|---|----------------------------------------------------------------------------------------------------------------------------------------|

|   | and Varification ]                                                                                                                     |

| References                            | Moni           | tored Pl | <u>i Verificat</u><br>atform Ele | ement     |          | Pur              | pose  |          |  |  |  |

|---------------------------------------|----------------|----------|----------------------------------|-----------|----------|------------------|-------|----------|--|--|--|

|                                       | μProc          | Mem.     | Comm.                            | Copr.     | Perfor.  | D&V <sup>c</sup> | Power | Security |  |  |  |

| State of the Art Academic Solutions   |                |          |                                  |           |          |                  |       |          |  |  |  |

| Nelissen et al. [31]                  | Х              |          |                                  |           |          | X                |       |          |  |  |  |

| Seo et al. [40]                       | Х              |          |                                  |           |          | Х                |       |          |  |  |  |

| Seo et al. [41]                       | Х              |          |                                  |           |          | Х                |       |          |  |  |  |

| Rambo et al. [35]                     | Х              |          |                                  |           | X        | Х                |       |          |  |  |  |

| Aldham et al. [4]                     | Х              |          |                                  |           | Х        |                  |       |          |  |  |  |

| Nadimpalli et al. [29]                | Х              |          |                                  |           | X        |                  |       |          |  |  |  |

| Scheipel et al. [39]                  | Х              |          |                                  |           | X        |                  |       |          |  |  |  |

| Sadek et al. [37]                     | Х              |          |                                  |           |          |                  | Х     |          |  |  |  |

| Patrigeon et al. [34]                 |                | Х        |                                  |           | X        |                  | Х     |          |  |  |  |

| Doyle et al. [13, 25]                 | Х              | Х        |                                  |           | X        |                  |       |          |  |  |  |

| Valente et al. [27, 44]               | Х              | Х        | Х                                |           | X        |                  |       |          |  |  |  |

| Kyung et al. [26]                     |                |          | Х                                |           | Х        |                  |       |          |  |  |  |

| Goeders et al. [16]                   |                | Х        | Х                                | Х         |          | Х                |       |          |  |  |  |

| Hammouda et al [17]                   |                | Х        |                                  | Х         |          | Х                |       | Х        |  |  |  |

| Fanni et. al [15, 24]                 | Х              |          |                                  | Х         | X        | Х                |       |          |  |  |  |

| Lee et al. [21]                       | Х              |          |                                  | Х         |          | Х                |       |          |  |  |  |

| Najem et al. [30]                     | Х              | Х        | Х                                | Х         |          |                  | Х     |          |  |  |  |

| Zoni et al. [11]                      | Х              | Х        | Х                                | Х         |          |                  | Х     |          |  |  |  |

|                                       | State o        | f the A  | rt Comm                          | ercial So | olutions |                  |       |          |  |  |  |

| ARM Coresight[6]                      | Х              | Х        | Х                                |           | X        | X                |       |          |  |  |  |

| Xilinx AXI PERF Mon [46] <sup>b</sup> |                |          | Х                                |           | Х        | Х                |       |          |  |  |  |

| Xilinx ILA [45] <sup>b</sup>          |                |          |                                  | Х         |          | X                |       |          |  |  |  |

| Altera SignalTap [5]                  |                |          |                                  | Х         |          | Х                |       |          |  |  |  |

| [THIS WORK]                           | X <sup>a</sup> | Xa       | Xa                               | X         | X        | X                | Х     | X        |  |  |  |

the addressed context. Our approach, as we already said, can certainly be considered cross-purpose since it focuses on the first two stages of the monitoring process formalized by Kornaros in [19], where the emphasis is not on metrics computation, but on gathering events to compute them.

It is worth noting that we are proposing a monitoring system targeting FPGA-based SoPCs that can be applied also to the monitoring of hardwired components. Indeed, the proposed monitor requires to access lines at RTL. When dealing with the monitoring of hardwired components, there can be two situations:

- the system manufacturer includes the proposed monitoring scheme in its RTL schematic during its design phases, finally merging it in the hardwired component;

- the lines to be monitored are accessible from an FPGA part present in the same SoC where the hardwired component lies.

In our work, we implement our monitor only on FPGAs because, except for layout activities and manufacturing, the rest of the flow is the same of hardwired components.

#### 111:8

## **3 THE PROPOSED MONITORING SYSTEM**

This section presents the paper contributions in detail. The first two subsections present the monitoring system and its features. In particular they:

- discuss the development of a HW monitoring system enforcing composability and homogeneous observability, by designing it as assembled by modules able to implement the generic monitoring process defined by Kornaros et al. [19]. Leveraging on the broadness of Kornaros' process, we ensure a wider applicability of the proposed solution;

- (2) review our previous work, AdaptIve Profiling Hardware Sub-system (AIPHS) [27, 44], originally applicable to microprocessors, interconnections, and memory, making it compliant to the newly proposed HW monitoring system;

- (3) present a comprehensive HW monitoring system, covering all the elements of the reference heterogeneous processing architecture, including the coprocessors.

The last subsection provides an example of implementation, presenting the design of the proposed monitoring system for a class of coprocessors existing in literature.

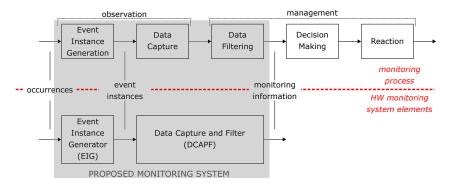

To build our monitoring system, we refer to the steps of a generic monitoring process, identified by Kornaros et al. [19], and reported in Figure 2. This figure highlights the contribution of the paper, which is the monitoring system, and the corresponding steps of the generic monitoring process it takes care of. The *Event Instance Generation* step takes as inputs the low-level signals describing occurrences happening on a platform and provides as output event instances, as defined in [31]. The *Data Capture* transforms the event instances into a meaningful representation that, after an opportune filtering in the *Data Filtering* step, can be aggregated to compute metrics (monitoring information) that satisfy given monitoring requirements. The monitoring information can be stored as result or forwarded to the *Decision Making* step, that in turn can decide whether to trigger a *Reaction* or not. To better depict the context of our work with respect to the generic monitoring process steps, we identify the two following categories:

- *Observation*: it includes the steps that extract information from executing targets, and organize them in metrics (monitoring information). The steps involved in this category are fully passive, meaning that the information is simply extracted but not used.

- *Management*: it includes the steps that, basing on the monitoring information, manage the system by applying countermeasures in case of deviations from given objectives. Then, the steps involved in this category can be considered active, since the extracted information is translated into decisions and actions over the system.

The proposed HW monitoring system mainly implements the steps part of the observation category and, for this, it can be efficiently used to support system-level methodologies that drive designers from requirements to ad-hoc monitoring systems (e.g., [41, 42]).

### 3.1 The Monitoring Process Implementation

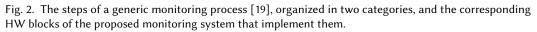

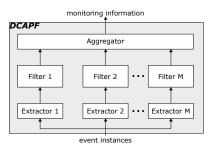

The *Event Instance Generation* step involves the generation of event instances when the low-level occurrences in a defined place of the target platform verify specific conditions. We implement this step by means of an Event Instance Generator (EIG) block. An EIG is composed of an Interfacer for the low-level occurrences, one or more Condition Checkers to evaluate if a specific condition is verified, and one Emitter to generate event instances (see Figure 3). The *Data Capture* step involves the management of event instances to obtain monitoring information. We implement this step and the *Data Filtering* step, with a Data CAPturer and Filter

Fig. 3. EIG HW block diagram.

(DCAPF) block *for each metric.* A DCAPF is composed of one or more Extractors to read event instances and format them in a suitable way to be aggregated, one or more Filters of the formatted data, and one Aggregator to exploit the filtered data to evaluate a metric (see Figure 4). The EIG and one or more DCAPF (depending on how many metrics are evaluated) are part of a *sniffer*, a HW component that takes as inputs low-level occurrences and outputs monitoring information.

Fig. 4. DCAPF HW block diagram.

The monitoring system is composed of distributed sniffers that make observable different system resources, at different abstraction levels. Each sniffer provides, as output, monitoring information following a given structure that is independent from the place where the monitoring information is extracted.

The level of customization provided through EIG and DCAPF within each sniffer, and their derivation from a generic monitoring process, offers the possibility to cover the different metrics that can be associated to functional objectives of monitoring considered in [19]. Furthermore, the splitting of the monitor in EIG and DCAPFs allows a

reuse of internal sniffer blocks among different monitoring systems.

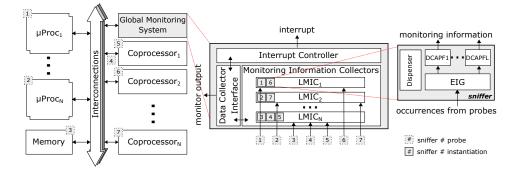

Fig. 5. HW block diagram of the complete monitoring system applied to the considered reference architecture.

J. ACM, Vol. 37, No. 4, Article 111. Publication date: August 2018.

The proposed sniffers deliver information to a Local Monitoring Information Collector (LMIC), as indicated in Figure 5, that controls the sniffers in a given local area, enabling or disabling them, and collecting their results.

LMICs are interfaced with the Interconnection through a Data Collector Interface (DCI) block that allows a homogeneous access to monitoring information coming from all the sniffers; to this end, the proposed monitoring system offers APIs to access monitoring information that can be used by any external host. It is worth noting that all the LMICs offer a unique shared register space. In order to efficiently bridging the steps of observation and management categories of the monitoring process (i.e., to avoid the polling of results), the proposed global monitoring system also offers the possibility to trigger an interrupt when thresholds are exceeded (by means of an Interrupt Controller, see Figure 5).

To clarify the implemented process in the creation of a sniffer, i.e., how to manage the usage of EIG and DCAPF, let us suppose that we are interested on monitoring all the writing transactions, between the addresses 0x0 and 0xF, happening on a given BUSx that connects memory mapped peripherals to multiple masters. The monitoring system will contain a single sniffer composed of an EIG and one DCAPF. In turn, the EIG will contain:

- an Interfacer, physically connected to the control and address lines of BUSx, to bring occurrences of the bus as input of Condition Checker;

- one Condition Checker, to verify whether the control lines in BUSx indicate a write. When the write happens, it is signalled to the Emitter;

- an Emitter to emit an event instance containing the address of the happened write and a sniffer identifier, when receiving the signalling from the Condition Checker,.

On the other hand, the DCAPF will contain:

- an Extractor, to receive event instances and extract useful data for the measure;

- one Filter, to check the addresses of the writes and keep the ones in the range of 0x0 0xF;

- an Aggregator, to aggregate the measures to get the monitoring information.

We have reviewed our previous work, AIPHS [27, 44], to make it compliant with the new proposed monitoring system. AIPHS is a HW monitoring system that observes the performance of a system by evaluating some metrics, and that is applicable to microprocessors, memories, and interconnections. Similarly to the proposed monitoring system, AIPHS is constituted of distributed sniffers controlled and read by a central element. Each sniffer is composed of an adapter, a nucleus, and an interface to receive commands and to send results. AIPHS is organized in a library fashion, in particular, there are three libraries containing elements: LIB\_ADAPT for the adapter, LIB\_NUCLEUS for the nucleus, and LIB\_GM for the interface.

*3.1.1 Implementation and Programmability Details.* In this section we provide a focus on implementation details, highlighting the configuration options, for the proposed monitoring solution blocks: the global monitor, the sniffers, and the DCAPF. Along with the descriptions, we also discuss which parts have been taken from AIPHS library, and which ones are new.

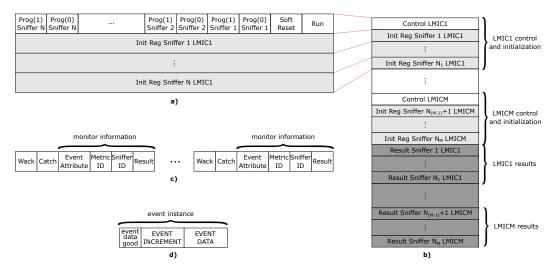

The global monitor interacts, through an interface connection, with a host that controls the monitoring process and makes usage of monitoring information. The global monitor is shown in the middle of Figure 5. The DCI receives the interface connection from host as input and propagates some control lines and initialization values to the different LMICs. Also, the DCI receives the sniffers results and makes them accessible through the interface connection toward the host. The DCI, depending on how it is configured, is able to either be accessed (in a slave fashion) or to automatically write (in a master fashion) monitoring information to an external memory. At least one LMIC must be present in the system, with at least one sniffer inside it. Three sets of registers

are available for each LMIC, namely the control, the initialization, and the results registers (see Figure 6.b). The control and initialization registers are organized as reported in Figure 6.a. The register on the top is the control one, that has the two least-significant bits assigned, respectively, to run and soft-reset. Moving to the most significative bits of the register, there are two programming bits associated to each sniffer; while, moving to bottom, there is an initialization register for each sniffer for the initialization of the value of the filtering range of the DCAPF (as detailed later in the section). To match with the number of sniffers inside the LMIC both the number of initialization registers as well as the number of bits used in the control register can be customized. Supposing that the control register is equal to 32 bit size, up to 15 sniffers can be connected to the LMIC. Results registers are accessible both by sniffers (to write monitoring information) and by the host through the interface connection (to read the monitoring information). Those registers are customizable in number and size, and each sniffer has its own private area to write its results. The ensemble of the LMIC registers represents the DCI register space, shown in the right-side of Figure 6.b. The global monitor and the DCI internal construction shall be manually performed by the users, but we provide a library of IP-cores to facilitate this action: in particular, we included in the new library different IP-cores already available from LIB GM of AIPHS, adding more IP-cores to provide the DCI with the capability of writing monitoring information toward a destination memory in a master fashion. In addition, the DCI now implements the management of Catch and Wack signals (detailed in the next paragraph), in order to better separate the communication among sniffers and the entities accessing (e.g., a microprocessor) the monitoring information.

Fig. 6. Data organization in the proposed monitoring system: a) control and initialization registers of the LMICs; b) DCI register space; c) structure of the sniffer output; d) structure of an event instance.

The sniffer is shown in the right side of Figure 5. It receives the occurrences as input, together with the control and initialization bus, and provides different monitoring information as output (depending on the number of DCAPFs), together with the *Catch* and *Wack* signals. The structure of the sniffer output is shown in Figure 6.c: each sniffer is able to output some monitoring information, associated to one or more DCAPFs. In particular, for each DCAPF, the sniffer outputs three information: *Wack* signal, *Catch* signal, and monitoring information. The latter is further divided in Event Attribute, that refers to attributes associated to the monitored events, Metric ID and Sniffer ID, that refer to the ID of the evaluated metric and the sniffer that provides it, respectively, and

Result, that refers to the metric value. Catch is high when the monitoring information is ready to be stored in the register of the DCI, while Wack is high when the monitoring information is ready to be accessed from the host. The necessity of two distinct phases, managed by Catch and Wack signals, comes from the fact that there are cases where the monitoring information is written in multiple steps, and only at the end it can be accessed. The programming bits for each sniffer have the following meaning:

- $PROG = \begin{cases} 00, & \text{IDLE the sniffer is not controlled neither by run nor soft-reset} \\ 01, & \text{INIT the sniffer initializes its internal DCAPF} \\ 10, & \text{FILTERING the sniffer works using its internal filters} \\ 11, & \text{NO-FILTERING the sniffer works without using its internal filters} \end{cases}$

When the run signal (coming from the LSB of Figure 6.a) is high, all the sniffers in FILTERING or NO-FILTERING mode connected to the corresponding LMIC start working. When the soft-reset signal (again coming from control register of Figure 6.a) is high, all the sniffers not in IDLE mode are internally reset. The EIG receives the occurrences as input and produces the event instances as output, as described above. Event instances have a well-defined structure, reported in Figure 6.d, where EVENT DATA represents the value associated to the monitored event, EVENT INCREMENT is the increment associated to the monitored event, and event data good, when high, ensures the validity of the event instance. The ratio behind the event instance structure is to produce an interconnection independent interface that provides both the EVENT DATA and a weight to count it (EVENT INCREMENT). The EIG strongly depends on the monitored interconnections (i.e., where the sniffer is connected and which kind of lines need to be monitored). The development of EIG internal blocks is left to users, and to support them we provide libraries with interfacers, condition checkers, and emitters IP-cores. In particular, we include in the new library different IP-cores already available from LIB\_ADAPT of AIPHS, adding new IP-cores to interface with AXI4-Full bus and to extract information from burst-based communication buses. Furthermore, as explained in the next section, we add also IP-cores to monitor coprocessors. The description of sniffer internal blocks ends with the dispenser, that receives some control lines (PROG, run, and soft-reset) and the initialization value associated to the sniffer, and propagates it to the DCAPF inside the sniffer. Each DCAPF requires two initialization values: due to the fact that the initialization register is unique for the sniffer, in order to initialize all the DCAPFs is required a number of writes that is two times the number of DCAPFs.

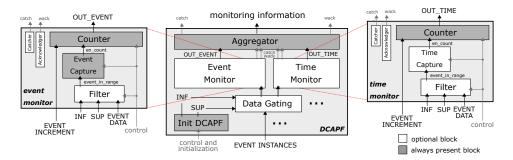

The DCAPF is shown in the middle of Figure 7. It receives control and initialization information, together with event instances, and produces monitoring information as output, together with Catch and Wack signals. With reference to Figure 7, the Event Monitor and Time Monitor are two blocks that represent two different Extractors. Both of them also contain the filters, as shown in the same Figure 7, on the left and on the right side. The Init DCAPF block stores the initialization values that represent the low and top of the range where filters work. The Data Gating block can be used if it is necessary to perform some gating actions on event instances, while the Aggregator block has been already discussed above.

The Event Monitor and Time Monitor are both shown in Figure 7, on the left and right side respectively. The Event monitor is able to count the number of event instances: depending on the presence or not of the filter, it also checks whether the EVENT DATA fits inside a range delimited by INF and SUP input values (they are included in the range). The Event Capture block ensures to add the event instance with the corresponding weight (EVENT INCREMENT) to the total event count (done with a counter). The Time Monitor has the same blocks of the Event Monitor, apart for Time

Fig. 7. DCAPF internal structure with a focus on time and event monitors.

Capture, that is able to measure the time spent within a range of values (selected using the Filter block). Finally, the Catcher and Acknowledger blocks provide the *Catch* and *Wack* signals. The development of DCAPF shall be made by users, even though leveraging on provided libraries with extractors, filters, and aggregators. In particular, the available extractors are the Time Monitor and the Event Monitor, discussed above, that have been taken from the LIB\_NUCLEUS of AIPHS and evolved toward a more reusable and configurable structure. In addition, both IP-cores optionally contain also catchers and acknowledgers.

The proposed monitoring system is highly configurable, thanks to the proposed libraries of IP-cores and their level of configurability. The IP-cores are provided through a VHDL description, and they can be configured using VHDL generics: they are all stored inside a VHDL configuration file, named *config.vhd*. Some of these generics are reported here below to build an example sniffer here named *WOT* (0 means that the block is not instantiated, 1 vice versa):

```

-- from the LSB, configure data gating block, time monitor, and event monitor

constant DCAPF_WOT_CONFIG: unsigned(4 downto 0) := "000";

-- from the LSB, configure filter, time capture block, catcher, and acknowledger

constant TIMEMON_WOT_CONFIG: unsigned(4 downto 0) := "0000";

-- size of the counter inside the event monitor

constant size_WOT_count_out_event: integer := 64;

-- size of the counter inside the time monitor

constant size_WOT_count_out_time: integer := 64;

```

APIs to use the monitoring system after its implementation are also available. An example of them is reported here below (the APIs details can be accessed in the jointer open-source repository [2]):

```

// initialize the selected DCAPF of the selected sniffer

void jointer_initialize(parameters)

// run sniffers of selected LMIC (works on FILTERING/NO-FILTERING sniffers)

void jointer_run(parameters)

// reset sniffers of selected LMIC (works on not IDLE sniffers)

void jointer_reset(parameters)

// print all the result registers of the selected LMICs

void jointer_print_reg(parameters)

```

#### 3.2 Extension to cover coprocessors

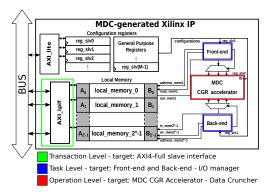

To extend the applicability of the proposed monitoring system to coprocessors, we leverage on a high-level architecture of a coprocessor, which internal architecture is divided in three main parts: Transaction Handler, I/O Manager and Data Cruncher. The Transaction Handler is responsible of interfacing each coprocessor with the interconnection backbone it is attached to. The I/O Manager is responsible of transferring the input data to the computing core of the coprocessor, which is the Data Cruncher, and to collect from it the results that will be transferred back to the host microprocessor through the Transaction Handler. Such a generic coprocessor architecture is quite common and it is adopted by different FPGA based computing heterogeneous platforms that embed

Fig. 8. MDC-based coprocessor, highlighted blocks are associated to different monitoring levels.

coprocessing units [20, 32, 36]. In such architectures three monitoring levels are possible:

- transaction level it applies to the logic within the Transaction Handler and is referred to the monitoring of all the HW elements inside the coprocessor that manage the transactions to interact, through the Interconnection, with other components of the reference architecture of Figure 1. As an example, the logic necessary to handle memory-mapped or stream-based transactions towards/from the microprocessors is monitored at transaction-level.

- task level it applies to the logic within the I/O Manager and is referred to the monitoring of all the HW elements inside the coprocessor that manage the start, the stop, and the I/O data of the executed HW-task. As an example, data movement from the coprocessor internal memory to/from the Data Cruncher are monitored at task-level.

- operation level it applies to the logic within the Data Cruncher and is referred to the monitoring of all the HW elements, at any granularity, inside the coprocessor that perform the computations associated to the HW-task. As an example, the individual functional units within the computing core of the coprocessor can be monitored at operation-level to check whether they represent a bottleneck for the computation by monitoring their busy/idle time.

By properly configuring the sniffers for the given coprocessors, we introduce a sniffer for each of the three levels that depends on (i) the occurrence to be observed and (ii) the metrics to be evaluated. For instance, for a HW monitoring system able to evaluate four different metrics, associated to a monitor for debugging [19] of the HW-tasks executed on a coprocessor, the metrics are expressed as follows:

- $METRIC_1^D$  total size of data transfers;

- $METRIC_2^{D}$  number of internal custom events referred to a generic computation;

- $METRIC_{3}^{D}$  time spent to perform a data transfer;

- $METRIC_{4}^{D}$  time spent to perform a computation;

The four metrics can be computed by collecting the following event instances:

- for *METRIC*<sup>D</sup><sub>1</sub>: a data transfer and the related amount of bytes is needed (transaction level);

for *METRIC*<sup>D</sup><sub>2</sub> an event inside the Data Cruncher is needed (operation level);

- for  $METRIC_3^D$  start and end of a data transfer are needed (transaction level);

- for  $METRIC_4^{\vec{D}}$  start and end of a computation within the coprocessor are needed (task level).

The four metrics can be computed by means of the three sniffers for the coprocessor monitoring.

If multiple clock regions are present in the system, very common situation in heterogenous platforms, the proposed approach is capable of collecting, storing and retrieving monitoring information in a consistent way. Coprocessors, which are one of the possible source of events/information in the proposed monitoring solution, usually run at different frequencies than microprocessors, that can act, for example, as monitoring information retrievers. According to the reference architecture depicted in Figure 5, sniffers connected to coprocessors extract event occurrences and extract monitoring information from them at the same frequency they are generated. Such information is then properly collected and stored by LMICs, and made available to the microprocessor through DCI, which can access to this latter at its own frequency. Thus, information collection and retrieving are completely decoupled, and can run at different speeds without problems, also leveraging on the possibility of adopting an interrupt mediated communication if reactivity is crucial.

In the next section, the design of the three sniffers for a class of coprocessors available from literature is reported, in order to highlight the reuse of components inside each sniffer.

#### 3.3 Implementation over a real coprocessor infrastructure

This section provides an example of implementation, over a microprocessor-coprocessor system, of the described HW monitoring system extension presented in Section 3.2.

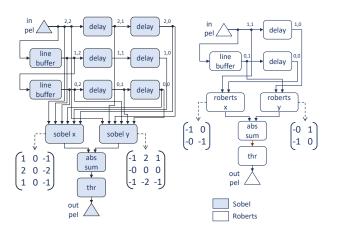

The class of coprocessors for which we implement the monitoring system is represented by coprocessors provided by the Multi-Dataflow Composer (MDC) tool, a dataflow to HW tool that automatically generates Coarse Grained Reconfigurable (CGR) HW designs [38]. Dataflows are oriented graphs whose nodes, the actors, are accounted for data processing, while the edges are point to point buffered communication channels. MDC takes as input dataflow network(s) specifications, combines them if they are more than one, and generates a ready-to-use IP. Depending on the number of input dataflows, MDC generates a non-reconfigurable (one dataflow) or CGR (more than one dataflow) coprocessor. In this second case, different dataflow specifications are merged together and different functionalities are enabled by multiplexing resources in time.

MDC has already been proven to be effective for the automatic instrumentation of the generated HW custom monitors. In the previous work of Fanni et al. [15], MDC-compliant coprocessors have been instrumented to be monitored, as already mentioned in Table 1. The HW block diagram of an MDC-generated coprocessor for Xilinx oriented platforms is reported in Figure 8, where we highlight the Transaction Handler, the I/O blue, and the Data Cruncher with green, black, and red colours, respectively. The coprocessor has an assigned data-set in memory and, when required by the host microprocessor, it streams data through a DMA, performs the computation within the Data Cruncher, and writes back results direct to memory. MDC-compliant coprocessors are interfaced with the rest of the computing platform through an AXI4 bus [7]. Therefore, the interface with the host microprocessor and with the on board memory is an AXI4 Slave Interface, representing the Transaction Handler block. Moreover, MDC-compliant coprocessors present a front-end and a back-end that, according to the chosen dataflow-based actor to actor communication protocol, are responsible of inputs management and outputs retrieval. Front-end and back-end, representing together the I/O manager, can be monitored to get task level information. HW tasks are executed within the MDC CGR accelerator that acts as the Data Cruncher.

In order to perform the monitoring process to compute the four metrics of the example reported at the end of the previous subsection, we designed the three sniffers capable of:

- collecting the total number of written and read bytes through the AXI4 Slave interface, monitoring transaction level information;

- measuring the time between the start and the end of a computation, monitoring task level information;

- collecting the total number of defined events, monitoring operation level information.

Fig. 9. Example of the proposed HW Monitoring System.

Capture and the Counter.

The operation level sniffer has an EIG that takes as input low-level coprocessor transactions associated to the CGR area, and provides as output event instances containing the number of events occurrences (with the EVENT INCREMENT) associated to specific events. The sniffer has multiple DCAPF, each one performing the counting of specific events. Each block contains the Init DCAPF, an Event Monitor, and an Aggregator. In turn, the Event Monitor contains the Event Capture and the Counter.

The final monitoring system, applied to MDC-based coprocessors, is reported in Figure 9. In this work, the implementation of the proposed HW monitoring system for coprocessors is partially

All the sniffers deliver their monitoring information to a single LMIC, while the DCI is an AXI4 Lite slave interface [7]. The host can access resulting monitoring information through a dedicated AXI4 Lite bus.

The transaction level sniffer has an EIG that takes as input low level AXI4 bus occurrences and provides as output event instances containing the address accessed for writing and reading as EVENT DATA, together with the associated number of bytes related to write/read bursts as EVENT INCREMENT. The sniffer has one DCAPF that accumulates the number of total written/read bytes that are performed on a predefined range. The block contains the Init DCAPF, an Event Monitor, and the Aggregator. In turn, the Event Monitor contains the Filter, the Event Capture, the Counter, and the Catcher.

The task level sniffer has an EIG that takes as input low-level coprocessor transactions associated to the Front-End and Back-End, and provides as output event instances containing the indication of a start of computation and end of computation (both as EVENT DATA). The sniffer has one DCAPF that measures the time between the start and the end of the computation, and provides that metric as output. The block contains the Init DCAPF, a Time Monitor, and an Aggregator. In turn, the Time Monitor contains only the Time automated. In particular, the coprocessor has been automatically generated and integrated in the microprocessor-coprocessor system using the MDC tool, while a Python script allows to modify the monitor configuration through a GUI, and, taking also into account the *config.vhd* file, to integrate the described sniffers, modifying the existing microprocessor-coprocessor system. Further details are reported in Section 4.2.3.

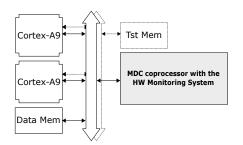

## 4 ASSESSMENT

In this section, we are going to assess the proposed monitoring system for the processing and coprocessing units considering a Xilinx Zynq-7000 XC7Z020 SoPC [47] (the coprocessing unit is compliant with the reference architecture presented in Figure 1, as discussed in Section 4.1). The assessment considers the dual-core ARM microprocessor and MDC-compliant coprocessors, and is performed in terms of provided degrees of freedom and customization possibilities on a simple fixed function coprocessor (see Section 4.2), and in terms of delivered benefits with respect to literature solutions on a more complex system with microprocessor and reconfigurable coprocessor (see Section 4.3).

## 4.1 Target Architecture and Experimental Setup

Figure 10 illustrates as the adopted device maps the elements of the reference architecture presented in Figure 1. In particular, the microprocessors are the two ARM Cortex-A9 cores, and the coprocessor is an MDC generated IP, as illustrated in Figure 8, connected to the microprocessors by means of a communication infrastructure that involves bus and Direct Memory Access engines (not represented for the sake of simplicity). The MDC CGR accelerator (please, refer to Figure 8) is the coprocessor Data Cruncher that, in this paper, can execute two applications, the Selective Accumulations (see Section 4.2) or the Edge Detection (see Section 4.3) one. Please note that, the main memory (Data Mem in Figure 10), where data to be processed and results are stored, for Resources and Dynamic Power data has been substituted with an AXI accessible BRAM memory. In all the other cases, it is an external DRAM. The monitoring system is composed of four sniffers, three for the MDC-based coprocessor, described in the previous section, and one for the ARM microprocessor. In particular, the sniffer for ARM is a sniffer that is able to observe a microprocessor that sends commands to an AXI4-Lite slave component. The AXI4-Lite slave component is represented by our monitoring system: when the microprocessor writes a value VAL in a specific memory location, the sniffer gets a timestamp and store a monitoring information constituted of VAL + TIMESTAMP in a dedicated memory. The dedicated memory is a BRAM (Tst Mem in Figure 10), and the microprocessor can access the monitoring information stored in BRAM again using the AXI4-Lite bus. A similar sniffer has been used in one of our previous works [28]: here, we reuse it by slightly changing the EIG block. All the sniffers are controlled by a single LMIC, while the DCI contains sixteen registers (each with a size of 32-bit). One register is left for the control associated to LMIC, while four are left for initialization of the four sniffers. The remaining eleven registers are used for the storage of monitoring information. In particular, the monitoring information related to the MDC-coprocessor are accessible by the host directly in the DCI registers, while the monitoring information related to the monitor for ARM are further stored in Tst Mem. The communication between the host (here, the ARM core microprocessor) and the global monitor is a dedicated AXI4-Lite bus. The host can access, using the same bus, to monitoring information stored in Tst Mem. Further details for the sniffers for MDC-based coprocessor are reported in the following:

• transaction level sniffer: collects the total number of written bytes by the coprocessor to the external memory. The size of the counter inside the Event Monitor is 23-bit. The sniffer writes its results to one of the DCI registers;

din forward mac\_16 mac\_16 mac\_16 dout 2 dout 1 dout 0

Fig. 10. Mapping of the Xilinx Zynq-7000 XC7Z020 over the reference architecture of Figure 1.

- task level sniffer: measures the duration, in terms of clock cycles, of the computation associated to the HW-task performed by the coprocessor. The size of the counter inside the Time Monitor is 53-bit size. The sniffer writes its results to two of the DCI registers, splitting the least and most significant parts of the result;

- operation level sniffer: collects the total number of selected events inside the Data Cruncher. The information on which are the selected events to be monitored, together with size of monitoring information, is reported below (since they vary from test to test).

The experiments reported hereafter have been carried out with the Xilinx Vivado design suite. Resources occupation data come from a full implementation of the considered designs under test, while the power consumption data have been obtained through Vivado power estimations by considering the real switching activity of the system, gathered during post-implementation functional simulations. Execution latency and memory footprint data have been measured during real executions on board. To reduce the statistical error, each latency number is computed as the average among 10 executions of the same design and configuration. Memory footprint numbers come from the actual memory occupancy of the SW part of the considered applications and from the amount of data due to HW-task execution and monitoring. The proposed monitoring system is designed in a way that it does not contain the system critical path (i.e., the addition of the monitoring system in the design does not impact in the maximum system clock frequency).

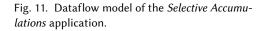

## 4.2 Exploration of the Monitoring Solutions

For a complete exploration of the possible monitoring solutions enabled by the proposed monitoring system, we here focus on the monitor customized to contain only the sniffer for MDC-based coprocessor, and we adopt an application that executes *Selective Accumulations* of input data to build a simple fixed function coprocessor. Figure 11 illustrates the dataflow representation of that application, which is composed of two actors:

- *forward* is responsible of data selection: it forwards data on a different output depending on the same data value (output 0 if input is bigger than 5, output 1 if input is between 0 and 4, output 2 if input is smaller than 0);

- *mac\_*16 is in charge of multiplying the input for a given constant and of accumulating together the result of 16 subsequent products (one different instance of such actor is connected to each output of *forward*).

The resulting HW coprocessor is the object of the assessment for the proposed monitoring.

*4.2.1 Designs Under Test.* In this exploration, we compare 10 different versions of the design under test (see Table 2). Different monitoring solutions are evaluated in different combinations of

| Design | Enable | d Moni | tor Level | Operation Level Configuration |                 |       |  |  |

|--------|--------|--------|-----------|-------------------------------|-----------------|-------|--|--|

| Design | trans. | task   | oper.     | #events                       | #bits per event | #regs |  |  |

| Y0     | -      | -      | -         | -                             | -               | -     |  |  |

| Y1     | x      | -      | -         | -                             | -               | -     |  |  |

| Y2     | -      | х      | -         | -                             | -               | -     |  |  |

| Y3     | -      | -      | Х         | 1                             | 5               | 1     |  |  |

| Y4     | -      | -      | Х         | 2                             | 10              | 1     |  |  |

| Y5     | -      | -      | Х         | 3                             | 20              | 3     |  |  |

| Y6     | x      | х      | -         | -                             | -               | -     |  |  |

| Y7     | x      | -      | х         | 2                             | 10              | 1     |  |  |

| Y8     | -      | х      | х         | 2                             | 10              | 1     |  |  |

| Y9     | x      | х      | х         | 2                             | 10              | 1     |  |  |

Table 2. Designs under test for the *Selective Accumulations* HW coprocessor involved in the exploration of the monitoring solutions (*trans.* and *oper.* are respectively *transaction* and *operation*).

sniffers and in different configurations to explore the possibilities available to the user to customize the monitoring system. Column *Enabled Monitor Level* illustrates the different combinations of sniffers (*transaction, task* and *operation* levels) that have been compared (*Y0* is the design without the monitoring system). Column *Operation Level Configuration* gives the details of the operation monitoring level. Column *#events* reports the number of different Data Cruncher events the sniffer is able to monitor. For each event, there is a dedicated DCAPF within the sniffer: column *#bits per event* reports the counter size of the Counter inside each Event Monitor contained in the DCAPF. Column *#regs* reports the register mapping. Please, notice that the adopted transaction level and operation level sniffers are a subset of the possible configurations. Indeed, the transaction level monitoring can be applied for different aspects of AXI transactions (e.g., number of read bytes or different address ranges), while the operation level monitoring can be applied for whatever event the designer needs to keep trace of within the HW coprocessor Data Cruncher. On the contrary, at the moment, besides counting events or monitoring time, the task level sniffer cannot be configured in a different manner.

| Design |      |       | Re   | esources |      |       |       | Dynamic | Power [n | nW]      |

|--------|------|-------|------|----------|------|-------|-------|---------|----------|----------|

| Design | LUT  | LUT%  | FF   | FF%      | BRAM | BRAM% | Exec. | Exec.%  | Transf.  | Transf.% |

| Y0     | 3397 | -     | 2864 | -        | 6    | -     | 24    | -       | 25       | -        |

| Y1     | 3675 | +8.18 | 3163 | +10.44   | 6    | +0.00 | 25    | +4.17   | 26       | +4.00    |

| Y2     | 3497 | +2.94 | 3092 | +7.96    | 6    | +0.00 | 25    | +4.17   | 26       | +4.00    |

| Y3     | 3478 | +2.38 | 3043 | +6.25    | 6    | +0.00 | 26    | +8.33   | 26       | +4.00    |

| Y4     | 3491 | +2.77 | 3058 | +6.77    | 6    | +0.00 | 25    | +4.17   | 26       | +4.00    |

| Y5     | 3516 | +3.50 | 3098 | +8.17    | 6    | +0.00 | 25    | +4.17   | 26       | +4.00    |

| Y6     | 3702 | +8.98 | 3217 | +12.33   | 6    | +0.00 | 27    | +12.50  | 28       | +12.00   |

| Y7     | 3690 | +8.63 | 3183 | +11.14   | 6    | +0.00 | 25    | +4.17   | 27       | +8.00    |

| Y8     | 3512 | +3.39 | 3112 | +8.66    | 6    | +0.00 | 26    | +8.33   | 26       | +4.00    |

| Y9     | 3718 | +9.45 | 3237 | +13.02   | 6    | +0.00 | 26    | +8.33   | 28       | +12.00   |

Table 3. Resources and power of the *Selective Accumulations* designs. *Exec.* refers to power consumption during coprocessor execution, while *Transf.* refers to power consumption during data transfer periods.

4.2.2 *Quantitative Results.* Table 3 depicts resource occupancy and power consumption results of the considered designs. Since the monitors are register-based, they present a cost in terms of *LUT*

| Design |        | Latenc | cy [us] |       | Memory [B] |         |      |       |  |

|--------|--------|--------|---------|-------|------------|---------|------|-------|--|

| Design | Tot.   | Tot.%  | Proc.   | Mon.  | Instr.     | Instr.% | Data | Data% |  |

| Y0     | 10.981 | _      | —       | —     | 229988     | _       | 204  | _     |  |

| Y1     | 14.356 | 30.73  | 10.839  | 4.617 | 235104     | 2.22    | 207  | 1.29  |  |

| Y2     | 14.736 | 34.20  | 10.804  | 5.128 | 235112     | 2.23    | 211  | 3.25  |  |

| Y3     | 14.161 | 28.96  | 10.597  | 4.692 | 235108     | 2.23    | 205  | 0.31  |  |

| Y4     | 14.831 | 35.06  | 10.853  | 5.207 | 235172     | 2.25    | 207  | 1.23  |  |

| Y5     | 15.122 | 37.71  | 10.806  | 5.365 | 235236     | 2.28    | 212  | 3.68  |  |

| Y6     | 15.083 | 37.36  | 10.861  | 5.278 | 235172     | 2.25    | 213  | 4.53  |  |

| Y7     | 15.172 | 38.17  | 10.813  | 5.593 | 235236     | 2.28    | 209  | 2.51  |  |

| Y8     | 15.08  | 37.33  | 10.567  | 5.685 | 235240     | 2.28    | 213  | 4.47  |  |

| Y9     | 15.338 | 39.68  | 10.574  | 5.945 | 235304     | 2.31    | 216  | 5.76  |  |

Table 4. Latency and memory footprint of the *Selective Accumulations* designs. *Instr.* is related to the whole executable file and *Data* is to the real disk occupancy of the data for processing and monitoring.

and *FF*, without any impact on the *BRAM* (we remark that we are considering only the monitor of MDC-based coprocessor here). This overhead is always under the 10% for *LUT* and 13% for *FF*. The lowest monitoring overhead is achieved by the *Y3* design, which employs only the operation level monitoring with 1 event (column *#events*) and a 5 bits counter (column *#bits per events*). The transaction level monitoring is the most resource hungry solution, since it embeds all the logic necessary for AXI protocol decoding and monitoring. Of course, when more than one monitoring level is enabled, the amount of overhead resources grows, up to the case where all the monitoring levels are employed (*Y9*).

Dealing with power numbers, a preliminary clarification is needed: the resolution of the power estimation is 1 mW, so that differences lying below this minimum value are lost. Power consumption presents only slight variations among different designs, variations sometimes even not expected, such as for *Y6* and *Y9* where this latter is consuming less than the former, which however demands more resources. It is mainly due to different synthesis and implementation choices that lead to optimizations under different goals: resource and/or timing for *Y6*, power for *Y9*. In terms of data transfer power (see *Transf.* column in the table), *Y6* and *Y9* have the same behaviour. Please note that power results almost follow the same trend of the resource ones, since *Y6* and *Y9* are still the most resource demanding solutions. Overall, the power overhead is small, since it is lower than 12.5% for both *Exec.* (coprocessor execution) and *Transf.* (data transfer) periods.